Portas Lógicas como entender

O Circuito Digital opera em dois Níveis de Tensão diferentes, Baixo e Alto. Geralmente, o Nível Baixo corresponde ao valor Lógico 0 e o Nível Alto corresponde ao valor Lógico 1. As Portas Lógicas são blocos de construção básicos na Electrónica Digital. A relação entre a(s) Entrada(s) e a Saída de uma Porta Lógica pode ser exprimida numa Tabela de Verdade.

Inversor, Porta NÃO (NOT Gate) e Seguidor (Buffer)

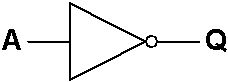

Um Inversor é uma Porta Lógica que tenha apenas uma Entrada. A sua Saída é o Estado Lógico complementar da sua Entrada. O Inversor é também designado como a Porta NÃO. O Símbolo Esquemático de um Inversor básico é mostrado na Figura 1 e a Tabela 1 é a sua Tabela de Verdade.

A notação da operação lógica de um Inversor pode ser expressa por:

Figura 1: Símbolo Esquemático do Inversor (Porta NOT)

| A | Q |

|---|---|

| 0 | 1 |

| 1 | 0 |

Tabela 1: Tabela de Verdade do Inversor (Porta NÃO)

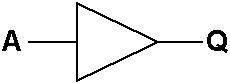

Um Seguidor é outra Porta Lógica com apenas uma Entrada, e a sua Saída segue o mesmo Estado Lógico da sua Entrada. O Seguidor é utilizado como um elemento de atraso na Electrónica Digital. É também um elemento para Esforçar a Corrente, que aumenta a capacidade de Saída de forma a conduzir outras portas. O Símbolo Esquemático de um Seguidor é mostrado na Figura 2 e a Tabela 2 é a sua Tabela de Verdade.

A notação da operação lógica de um Seguidor pode ser expressa por:

Figura 2: Símbolo Esquemático do Seguidor

| A | Q |

|---|---|

| 0 | 0 |

| 1 | 1 |

Tabela 2: Tabela de Verdade do Seguidor

Portas NÃO E (NAND) e E (AND)

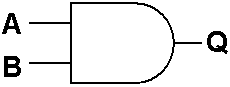

Uma Porta E é uma Porta Lógica que tem duas ou mais Entradas. A sua Saída é 1 se e só se todas as suas Entradas são 1. O Símbolo Esquemático de uma Porta E com Duas Entradas é mostrado na Figura 3 e a Tabela 3 é a sua Tabela de Verdade.

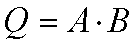

A notação da operação lógica de uma Porta E pode ser expressa por:

Figura 1: Símbolo Esquemático da Porta AND

| A | B | Q |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Tabela 3: Tabela de Verdade de uma Porta E (AND)

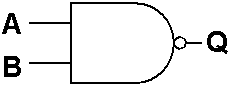

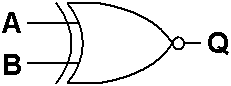

Uma Porta NÃO E é uma Porta Lógica que tem duas ou mais Entradas. A sua Saída é 0 se e só se todas as suas Entradas são 1. O Símbolo Esquemático de uma Porta NÃO E com Duas Entradas é mostrado na Figura 4 e a Tabela 4 é a sua Tabela de Verdade.

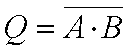

A notação da operação lógica de uma Porta NÃO E pode ser expressa por:

Figura 4: Símbolo Esquemático da Porta NAND

| A | B | Q |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Tabela 4: Tabela de Verdade de uma Porta NÃO E (NAND)

Portas NÃO OU (NOR) e OU (OR)

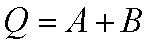

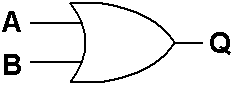

Uma Porta OU é uma Porta Lógica que tem duas ou mais Entradas. A sua Saída é 0 se e só se todas as suas Entradas são 0. O Símbolo Esquemático de uma Porta OU com Duas Entradas é mostrado na Figura 5 e a Tabela 5 é a sua Tabela de Verdade.

A notação da operação lógica de uma Porta OU pode ser expressa por:

Figura 5: Símbolo Esquemático da Porta OR

| A | B | Q |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

Tabela 5: Tabela de Verdade de uma Porta OU (OR)

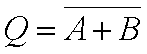

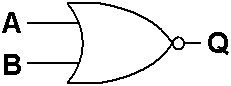

Uma Porta NÃO OU é uma Porta Lógica que tem duas ou mais Entradas. A sua Saída é 1 se e só se todas as suas Entradas são 0. O Símbolo Esquemático de uma Porta NÃO OU com Duas Entradas é mostrado na Figura 6 e a Tabela 6 é a sua Tabela de Verdade.

A notação da operação lógica de uma Porta NÃO OU pode ser expressa por:

Figura 6: Símbolo Esquemático da Porta NOR

| A | B | Q |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

Tabela 6: Tabela de Verdade de uma Porta NÃO OU (NOR)

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Circuitos Práticos de Testes de portas lógicas

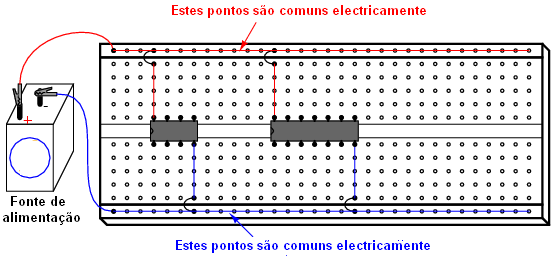

Os circuito digitais testados vão usar tecnologia CMOS, por esse motivo os circuitos integrados permitem uma variação maior de tensão com um consumo mais reduzido. Os circuitos CMOS são susceptíveis de ficarem danificados com electricidade estática, tome as precauções adequadas se pretende testar estes circuitos.

Circuitos usando tecnologia TTL têm de ter uma fonte de alimentação com 5V, não toleram uma variação significativa destes valores.

Para os testes práticos vamos usar uma placa de testes.

Funções básicas das portas lógicas

Componentes e materiais

- 4011 quad NAND gate

- Eight-position DIP switch

- Ten-segment bargraph LED - Normalmente os leds usados nos vuímetros

- Bateria ou Fonte de alimentação de 6V

- Duas resistências 10 kΩ

- Três resistências 470 Ω

Atenção! O 4011 IC é CMOS, é por isso sensível a descargas electricas estáticas!

Comentários